인텔(Intel)이 업계 최초의 고대역폭 메모리 통합 FPGA를 선보였다.

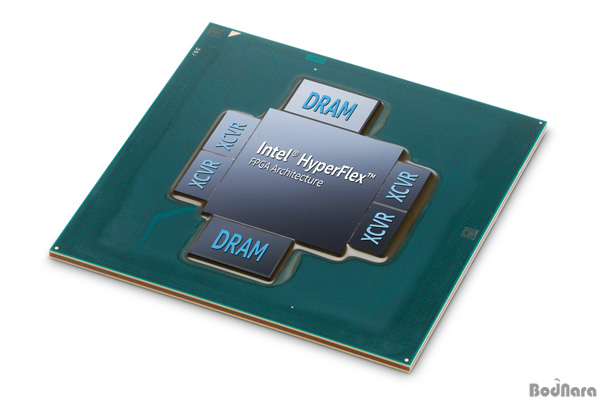

인텔은 18일(현지시간) 보도자료를 통해 고 대역폭 D램(HBM2)을 통합한 업계 최초의 FPGA (Field Programmable Gate Array) 제품인 Stratix 10 MX FPGA를 출시한다고 밝혔다.

인텔 Stratix 10 MX FPGA는 14nm FinFET 공정으로 만들어지며 TSV 기술을 사용해 D램 레이어를 수직으로 쌓아올린 HBM2 메모리를 FPGA와 통합함으로써 일반적인 독립형 DDR 메모리 솔루션을 가진 제품과 비교해 최대 10배 달하는 512GB/s의 대역폭을 제공하는 것이 특징이다. 이 D램 레이어는 고밀도 마이크로 범프를 사용해 FPGA에 연결되는 기본 레이어에 배치된다.

인텔 Stratix 10 MX FPGA 제품군은 FPGA 패브릭과 D램 사이의 통신을 가속화하는 인텔의 임베디드 멀티 다이 상호 연결 브릿지(EMIB)를 사용해 HBM2을 고성능 모놀리식 FPGA 패브릭과 효율적으로 통합해 메모리 대역폭 병목 현상을 전력 효율적으로 해결한다.

이러한 높은 메모리 대역폭을 이용해 대량의 데이터 이동 및 스트림 데이터 파이프라인 프레임 속도를 높이기 위한 하드웨어 가속기가 요구되는 고성능 컴퓨팅(HPC), 데이터 센터, 네트워크 기능 가상화, 방송 애플리케이션 분야에 활용될 수 있다.

인텔은 HPC 환경에서는 대용량 데이터 이동 전후에 데이터 압축 및 해제 기능이 가장 중요하며 ,HBM2 기반 FPGA가 독립형 FPGA에 비해 더 큰 데이터 이동을 압축하고 가속화 할 수 있다고 설명했다. 또한 고성능 데이터 분석(HPDA) 환경에서 Apache Kafka 및 Spark Streaming 같은 스트리밍 데이터 파이프라인 프레임워크에 호스트 CPU 리소스에 부담을 주지 않으면서 실시간으로 데이터를 읽고 쓰고 암호화를 할 수 있다고 언급했다. |