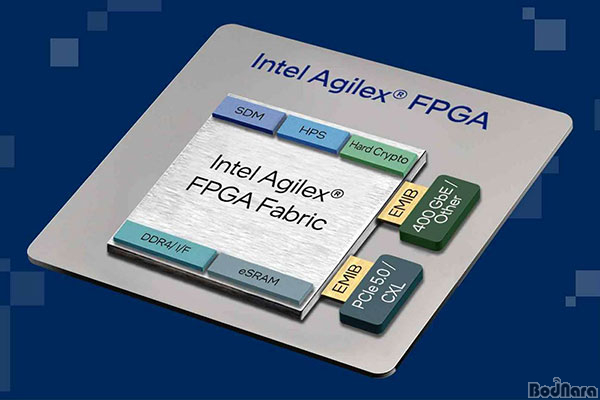

인텔 프로그래머블 솔루션 그룹은 R-타일이 내장된 인텔 애질렉스® 7(Intel Agilex® 7)을 양산 및 출하한다고 25일 밝혔다. 애질렉스 7은 FPGA 최초로 PCIe 5.0 및 컴퓨트 익스프레스 링크(CXL) 기능과 해당 인터페이스를 지원하는 하드IP(Hard IP)를 제공한다.

시간, 예산, 전력 등 제약사항에 직면한 데이터 센터, 통신, 금융서비스를 비롯한 여러 산업 분야에서는 유연하고 프로그래밍 가능하며 효율적인 솔루션으로 FPGA를 선택하고 있다. 기업은 R-타일이 내장된 애질렉스 7을 사용해 최고 대역폭 프로세서 인터페이스를 갖춘 4세대 인텔® 제온® 스케일러블 프로세서 같은 프로세서와 FPGA를 원활하게 연결하여 타겟 데이터 센터 및 고성능 컴퓨팅 워크로드를 가속화할 수 있다. 더불어, 애질렉스 7의 구성 및 확장 가능한 아키텍처를 통해 특정 요구사항 및 하드웨어 속도에 따라 맞춤형 기술을 대규모로 신속하게 배포해 전체 설계 비용과 개발 프로세스를 절감하고 실행 속도를 높여 최적의 데이터 센터 성능을 달성할 수 있다.

R-타일 내장 애질렉스 7 FPGA는 경쟁사 제품 대비 2배 빠른 PCIe 5.0 대역폭과 포트당 4배 높은 CXL 대역폭 등 선도적인 기술 역량을 제공한다. 메타(Meta)와 미시간 대학교(University of Michigan)가 발표한 백서에 따르면 4세대 인텔 제온 스케일러블 프로세서 기반 서버에 CXL 메모리가 탑재된 FPGA를 추가하고 동시에 효율적인 투명 페이지 배치(TPP: Transparent Page Placement)를 사용할 경우 리눅스 성능이 최대 18% 상승한다. 또한, 유니패브릭스(UnifabriX)는 고성능 컴퓨팅 워크로드를 위해 2배 많은 4세대 인텔 제온 스케일러블 프로세서를 사용하면서 HPCG 벤치마크 점수를 28% 향상하는 등, 여러 벤치마크에서 CXL 지원 스마트 메모리 노드를 시연했다.

더 많은 정보: 제품 및 구매에 대한 자세한 내용은 블로그에서 확인할 수 있다.

|