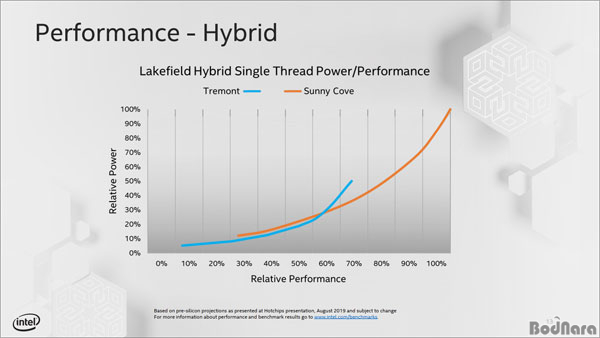

| РЮХкПЁМ ЛѕЗЮПю РњРќЗТ ЧСЗЮМММ ОЦХАХиУГРЮ ЦЎЗЙИѓЦЎИІ АјНФ ЙпЧЅЧпДй.

РЮХкРЧ ЛѕЗЮПю 3D ЦаХАТЁ БтМњРЮ ЦїКЃЗЮНК(Foveros)ЗЮ МГАшЕШ ЦЎЗЙИѓЦЎ(Tremont)ДТ РќРлКИДй АэМКДЩРЛ ЙпШжЧЯИщМ КЙРтЧб

ПіХЉЗЮЕхИІ ЦјГаАд СіПјЧЯБтРЇЧи НЬБл НКЗЙЕх МКДЩРЛ ГєРЬАэ, 5G ГзЦЎПіХЗАњ ХЌЖѓО№ЦЎ, ЙшХЭИЎ АцЧш АГМБРЛ УпБИЧпДй.

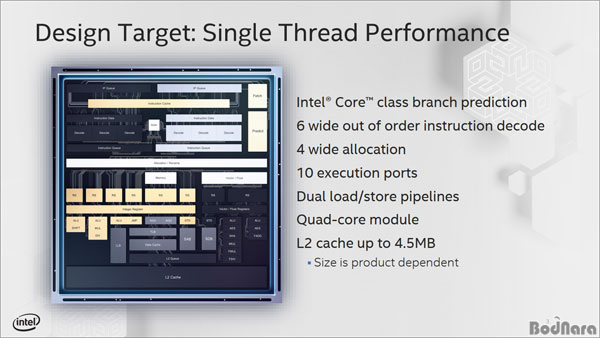

ЦЎЗЁИѓЦЎРЧ РќМККёДТ 10ММДы ФкОю ЧСЗЮМММ ОЦРЬНК ЗЙРЬХЉРЧ ЦЏСЄ ПЕПЊПЁМ РЏЛчЧб ЦаХЯРЛ КИПЉСжИч, ФкОю ЧСЗЮМММПЁ СиЧЯДТ КаБт ПЙУјАњ

6wide КёМјТї ИэЗЩ Е№ФкЕх, 10 НЧЧр ЦїЦЎ, ФѕЕх ФкОю И№Ет, УжДы 4.5MBРЧ L2 ФГНУ, ЕрОѓ ЗЮЕх/ НКХфОю ЦФРЬЧСЖѓРЮ БИСЖИІ АЎУшДй.

ХИАйУўПЁ ИТУч ЧСЗаЦЎ ПЃЕх Е№ФкЕх ДмПЁМ НЬБл ХЌЗЏНКЦЎ И№ЕхИІ СіПјЧЯИч, НЧЧр РЏДжРК 3ALUПЭ 2AGU, 1 НКХфОю РЏДж, 1JMPЗЮ

БИМКЕЧИч, 200 РЬЛѓРЧ ОЦПє ПРКъ Дѕ РЉЕЕПь ПЃЦЎИЎ, 6 КДЗФ ПЙОр НКХзРЬМЧРЛ АЎУшДй. ЙщХЭ НЧЧрАњ АќЗУЧи КИОШ АШИІ РЇЧи 4ЛчРЬХЌРЧ ЕрОѓ

128b AES РЏДж, 4ЛчРЬХЌРЧ НЬБл ИэЗЩ SHA256, КДЗЩ ПЙОр НКХзРЬМЧ 2АГ, НЧЧр ЦїЦЎ 3АГИІ СІАјЧбДй.

ИоИ№ИЎ НЧЧрРК ЕрОѓ ЗЮЕх/ НКХфОю ЦФРЬЧСЖѓРЮПЁ 32BK ЕЅРЬХЭ ФГНУДТ ЛчПыРЛ РЇЧб ЗЮЕхПЁ 3ЛчРЬХЌРЬ МвПфЕЧИч, ФкЕхПЭ ЕЅРЬХЭИІ

АјРЏЧЯДТ 1024 ПЃЦЎИЎ ММФС ЗЙКЇ TLBИІ СіПјЧбДй. ФкОюАЃ АјРЏИІ РЇЧб L2 ФГНУДТ 1.5MBПЁМ 4.5MBБюСі СЖР§ЕЧИч, LLCДТ

InclusivПЭ non-InclusiveИІ СіПјЧбДй.

ЛѕЗЮПю ШПРВ АГМБРЛ РЇЧб ЛѕЗЮПю УпЗа ИэЗЩОюПЭ ЧЯЕхПўОю БтЙн ХЌЗА СЖР§ БтМњРЮ НКЧЧЕх НУЧСЦЎ, КИОШРЛ РЇЧб РЮХк НХЗк НЧЧр БтМњАњ КЮЦЎ

АЁЕх, ЙАИЎРћ АјАн ДыРРРЛ РЇЧб РЮХк ХфХЛ ИоИ№ИЎ ОЯШЃШ БтМњЕЕ СіПјЧбДй.

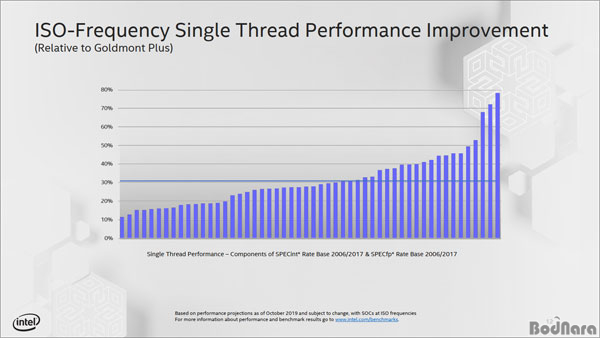

РЮХкРК ЦЎЗЙИѓЦЎДТ РќММДы РњРќЗТ x86 ЧСЗЮМММ ДыКё IPC АГМБПЁ С§Сп, ЦїКЃЗЮНК 3D ЦаХАТЁРЛ ХыЧи АЗТЧб МКДЩРЛ ФФЦбЦЎЧб РњРќЗТ

ЦаХАТЁРЛ БИЧіЧЯДТЕЅ МКАјЧпДйАэ ЙпЧЅЧпСіИИ, БИУМРћРИРИЗЮ РќММДыПЭ КёБГЧи ОюДР СЄЕЕРЧ АГМБРЬ РЬЗяСГДТСіПЁ ДыЧиМДТ ИЛРЛ ОЦВМДй.

ЧбЦэ, РЮХкРЧ ЙпЧЅПЁ ЕћИЃИщ ЦЎЗЁИѓЦЎ ОЦХАХиУГДТ БйЗЁ ЙпЧЅЕШ ИЖРЬХЉЗЮМвЧСЦЎ МЧЧНК ГзПРПЁ ХОРчЕШ ЗЙРЬХЉЧЪЕх IPПЁ УГРН РћПыЕШДй. МЧЧНК

ГзПРРЧ ПЙЛѓ УтНУРЯРК 2020Гт ШІИЎЕЅРЬ НУС№РИЗЮ, НЧСІ ЦЎЗЁИѓЦЎ ОЦХАХиУГРЧ ЗЙРЬХЉЧЪЕхАЁ РћПыЕШ СІЧАРК ЛЁЖѓОп ГЛГтПЁГЊ ИИГЊКМ АЭРИЗЮ ПЙЛѓЕЧИч,

РЬАЭРЬ РќММДы ДыКё АГМБЦјПЁ ДыЧи ИЛРЛ ОЦГЄ РЬРЏЗЮ ЦЧДмЕШДй.

|