비아 (VIA)는 x86 프로세서와 이를 지원하는 칩셋을 개발하고 임베디드 시장을 타겟으로 한 다양한 플랫폼을 출시해왔는데 빠르게 성장하고 있는 SSD (Solid State Drivers) 시장을 위해 Tensilica의 SoC (System On Chip)로 이루어진 Xtensa Dataplane Processors (DPUs) 아키텍처를 채택했다고 xbitlabs는 전했다.

SSD 장치는 빠르고 효율적인 데이터 관리, 그리고 입출력 (IOPS, input/output operations per second) 성능이 우수하며, 높은 신뢰성과 저전력으로 동작된다. 이를 위해서는 낸드 플래시 (NAND Flash) 기술 뿐만 아니라 이를 제어하는 SSD 컨트롤러의 영향이 크게 작용한다.

비아가 Tensilica로부터 라이센스받은 Xtensa DPUs는 경쟁 SSD 컨트롤러 대비 4배 이상의 높은 처리 성능을 제공한다고 전했다.

비아의 Jiin Lai CTO (Chief Technology Officer)는 SSD 시장은 매우 경쟁력있고 수익 높은 시장으로 우리에게 매우 중요하며, 비아는 Tensilica의 Xtensa DPUs를 바탕으로 저전력과 입출력 성능이 향상된 제품을 개발할 것이라고 밝혔다.

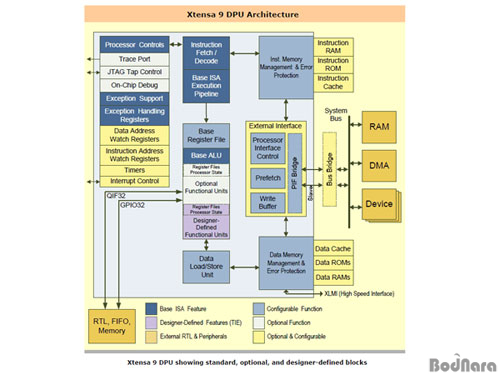

Tensilica의 Xtensa DPUs는 RISC 기반 IP Core를 커스터마이징 가능하며, 컨트롤 및 신호 프로세싱 통합, 고대역의 연결을 추가해 클럭 속도 향상 없이 성능을 향상시킬 수 있도록 최적화가 이루어졌다. 기존 프로세서는 성능을 높이는데 클럭 향상을 이용하나 이는 전력 사용량 증가와 다이 사이즈 증가를 가져온다.

또한 내부 처리 개선으로 다른 경쟁 프로세서보다 10배 이상의 효율과 IOPS 및 전력 소비 감소 등의 이점을 제공할 것이라고 전했다. |